14++ Placement stage in vlsi ideas

Home » money laundering idea » 14++ Placement stage in vlsi ideasYour Placement stage in vlsi images are available. Placement stage in vlsi are a topic that is being searched for and liked by netizens today. You can Find and Download the Placement stage in vlsi files here. Find and Download all royalty-free vectors.

If you’re looking for placement stage in vlsi pictures information connected with to the placement stage in vlsi keyword, you have visit the ideal site. Our site always provides you with hints for seeking the highest quality video and picture content, please kindly surf and locate more enlightening video content and graphics that match your interests.

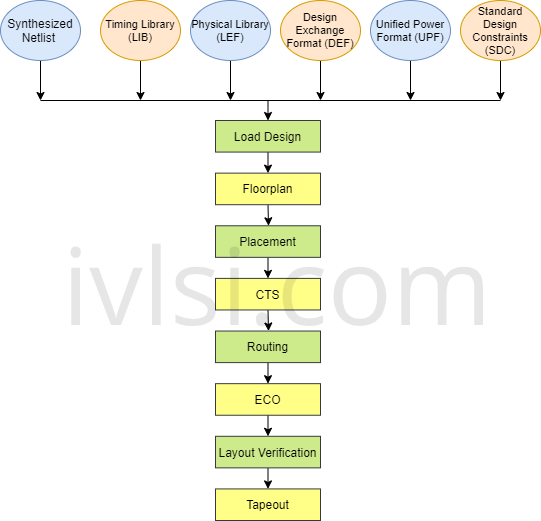

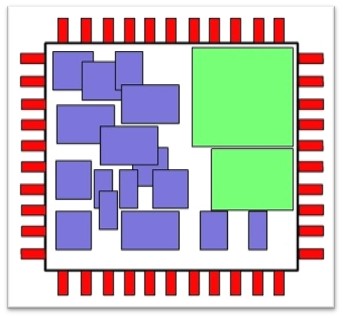

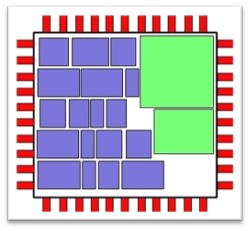

Placement Stage In Vlsi. Placement is a very important stage of physical design where all the standard cells get placed inside the core boundary. We synthesize clocks in the next stage ie. High fanout net synthesis. Placement largely determines the length and hence the delay of interconnects wires.

The Two Stage Placement Flow Download Scientific Diagram From researchgate.net

The Two Stage Placement Flow Download Scientific Diagram From researchgate.net

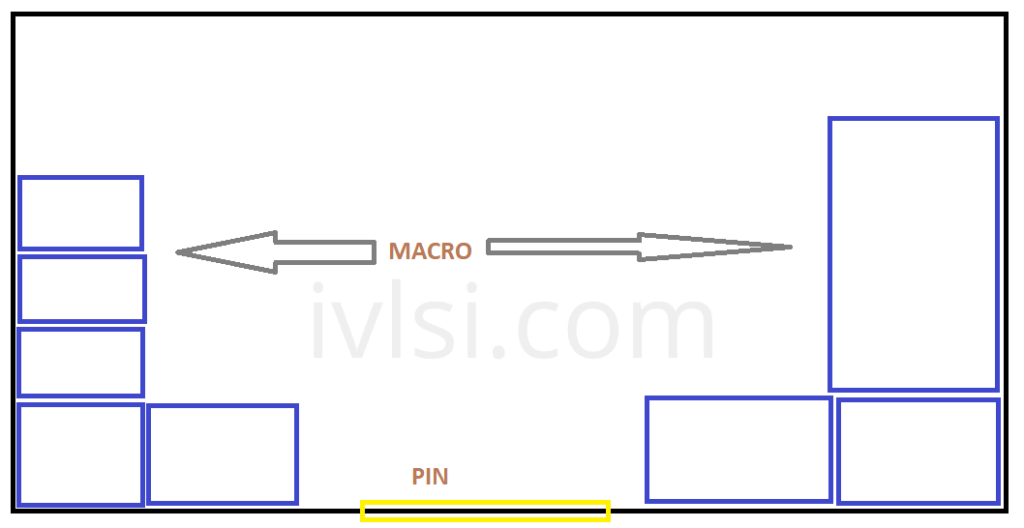

Placement will be driven by different criteria like timing drivencongestion driven and power optimization. Legalization makes the rough solution from global placement legal no placement constraint violation by moving modules around locally. In logic synthesis high fanout nets like reset scan enable etc are not synthesized. Placement is a step in the Physical Implementation process of placing the standard cell in a standard cell rows in order meet the timing congestion and utilization. Placement takes place in two steps. Special Cell Placement - Placement of Well-Tap Cells End-Cap Cells Spare Cells Decap Cells JTAG and Other Cells Close to the IOs 2.

For best results make the number of cells you place in placement bounds relatively small compared to the total number of cells in the design.

Minimal cell density and pin density. Overall QoR of the design greatly depends on the fact that how well placement is done. It also optimizes the design thereby removing any timing violations created due to the relative placement on die. Tool legalize the placement. Placement is a very important stage of physical design where all the standard cells get placed inside the core boundary. Placement is done in three steps.

Source: researchgate.net

Source: researchgate.net

Placement is a very important stage of physical design where all the standard cells get placed inside the core boundary. Legalization makes the rough solution from global placement legal no placement constraint violation by moving modules around locally. Once we are done with the floorplan after placing all the physical cells inside the core boundary we are left with standard cells which are still sitting out of the core design area. It also optimize the design. Special Cell Placement - Placement of Well-Tap Cells End-Cap Cells Spare Cells Decap Cells JTAG and Other Cells Close to the IOs 2.

Source: ivlsi.com

Source: ivlsi.com

Friday February 14 2020. Placement will be driven by different criteria like timing driven congestion driven power optimization. Definition Placement is the process of placing standard cells in the rows created at floor planning stage. Final phase of path optimization to improve timing. For best results make the number of cells you place in placement bounds relatively small compared to the total number of cells in the design.

Source: signoffsemi.com

Source: signoffsemi.com

You must have noticed that the placement stage takes quite a large runtime. We synthesize clocks in the next stage ie. Placement is done in three steps. This is the command syntax. Areatiming and power optimizations.

Source: teamvlsi.com

Source: teamvlsi.com

Friday February 14 2020. Interview question related to placement - VLSI- Physical Design For Freshers. Placement does not just place the standard cell available in the synthesized netlist. Perform incremental timing area congestion and leakage power optimization. VLSI - Physical Design.

Source: vlsibegin.blogspot.com

Source: vlsibegin.blogspot.com

We synthesize clocks in the next stage ie. Legalization makes the rough solution from global placement legal no placement constraint violation by moving modules around locally. Overall QoR of the design greatly depends on the fact that how well placement is done. Also it is not performed on dont touch attribute nets. We synthesize clocks in the next stage ie.

Source: teamvlsi.com

Source: teamvlsi.com

Plaement Methodology - Congestion Driven Placement Timing Driven Placement 4. Optimizing and Reordering Scan Chains 3. Plaement Methodology - Congestion Driven Placement Timing Driven Placement 4. This is the command syntax. Now we need to place all the standard cell sitting outside this core boundary.

Source: ivlsi.com

Source: ivlsi.com

Placement is done in three steps. Placement will be driven by different criteria like timing driven congestion driven power optimization. High fanout nets other than clocks are synthesized at the placement stage. This is the command syntax. Placement is a very important stage of physical design where all the standard cells get placed inside the core boundary.

Interview question related to placement - VLSI- Physical Design For Freshers. It is the third step in Physical design flow. Placement largely determines the length and hence the delay of interconnects wires. It also optimizes the design thereby removing any timing violations created due to the relative placement on die. Overall QoR of the design greatly depends on the fact that how well placement is done.

Minimal cell density and pin density. Plaement Methodology - Congestion Driven Placement Timing Driven Placement 4. Below are key task perfomed during Placement stage 1. Global placement generate a rough placement that may violate some placement constraints eg there may be overlaps among modules 2. Overall QoR of the design greatly depends on the fact that how well placement is done.

Source: teamvlsi.com

Source: teamvlsi.com

VLSI - Physical Design. Since clock nets are considered ideal at placement stage HFNS is not performed on clock nets even though they are High Fanout Nets. Placement is a critical step in VLSI design flow mainly for the following four reasons. Placing of these standard cells is called placement stage. Optimizing and Reordering Scan Chains 3.

Make sure to define clocks as ideal in the placement stage otherwise HFNS will be done on the clock. Below are key task perfomed during Placement stage 1. Optimizing and Reordering Scan Chains 3. Now we need to place all the standard cell sitting outside this core boundary. Placement is a very important stage of physical design where all the standard cells get placed inside the core boundary.

Source: researchgate.net

Source: researchgate.net

Tool determine the location of each of the standard cell on the die. During Placement all standard cells are placed automatically on the chip core based on timing die size and power constraints. This is the command syntax. Legalization makes the rough solution from global placement legal no placement constraint violation by moving modules around locally. Placement will be driven by different criteria like timing drivencongestion driven and power optimization.

Source: vlsibegin.blogspot.com

Source: vlsibegin.blogspot.com

In this stage all the standard cells are placed in the design. In this stage all the standard cells are placed in the design. Placement largely determines the length and hence the delay of interconnects wires. Placement does not just place the standard cell available in the synthesized netlist. Make sure to define clocks as ideal in the placement stage otherwise HFNS will be done on the clock.

This site is an open community for users to share their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site helpful, please support us by sharing this posts to your preference social media accounts like Facebook, Instagram and so on or you can also save this blog page with the title placement stage in vlsi by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.